今回は基本情報技術者試験のコンピュータ構成要素について説明しようと思います。一回ですべて説明しようとすると長くなるので数回に分けて説明していきたいと思います。

用語

- プログラム記憶方式:CPUが主記憶から順に読み出し実行

- クロック信号:CPUが発する周期的な信号

- バス:データのやり取りをする伝送路

- バス幅:1クロックのデータ量

- レジスタ:CPU内部の記憶装置(各種の説明はこれを押せば飛びます)

- 命令実行サイクル:←押して図を見た方が分かりやすい

- アドレス指定方式:←で図入りで見た方がいい

- 逐次制御方式:命令を1つずつ実行

- パイプライン方式:命令を1ステージずつずらして実行

- スーパーパイプライン方式:パイプライン方式のステージを細分化

- スーパースカラ方式:同時に複数の命令を実行

- CISC:複雑な命令体系

- RISC:単純な命令体系

- マルチプロセッサ:1つのCPUに複数のコア

- GPU:行列演算強い

コンピュータの基本構成

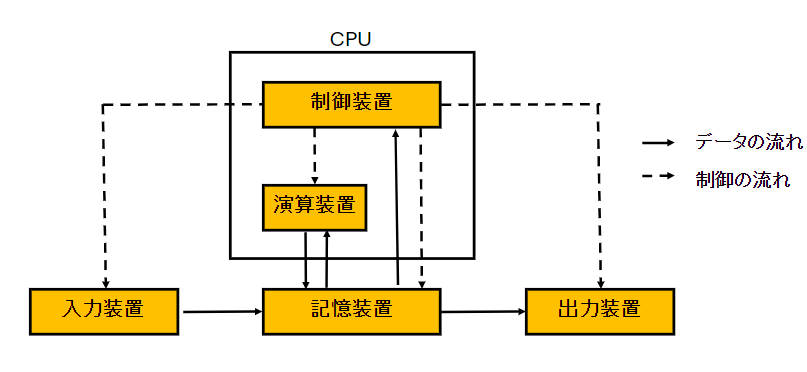

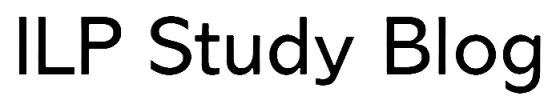

コンピュータは、CPU(制御装置、演算装置)、記憶装置、入力装置、出力装置の5つから構成されています。それぞれについて説明したものが、下記とその下の図になります。

- 制御装置:各装置の制御を行う装置のことをいい、下図では「制御装置」から「制御の流れ」の矢印が各装置に向かうことで表現されています。

- 演算装置:演算(四則演算や論理演算)を行う装置のことをいい、この「演算装置」と「制御装置」が一体となった機器のことをCPUといいます。

- 記憶装置:データを保存する装置のことをいい、主記憶装置と補助記憶装置があります。主記憶装置としてはRAM(メモリ)、補助記憶装置としては磁気ディスク(HDD)などが例として挙げられます。

- 入力装置:コンピュータに外部から入力を行う装置のことをいい、キーボードやマウスなどが例として挙げられます。

- 出力装置:コンピュータの内部で行われた処理を外部へ出力する装置のことをいい、ディスプレイなどが例として挙げられます。

主記憶装置に記憶されたプログラムを、CPUが順に読み出しながら実行する方法をプログラム記憶(格納)方式といいます。プログラムを変更するだけで様々な処理を行えることから、現在のコンピュータのほとんどは採用している方式になります。

CPU

ここからは、上記で軽く触れたCPUについて説明していきます。CPUはプロセッサと呼ばれることもあり、制御装置や演算装置、レジスタなどから構成されています。CPUが発する周期的な信号をクロック信号といい、このクロック信号が1秒間に繰り返される回数をクロック周波数といいます。このクロック周波数が高いほど処理能力が高くなるのですが、同時にCPUの発熱量も増加してしまいます。

CPU内部のクロック周波数を内部クロック、CPUと各装置を結ぶ経路の周波数のことを外部クロックといいます。この内部クロックと外部クロックは同じである必要がなく、内部クロックが外部クロックの数倍で動作させていたりします。

コンピュータの中でデータをやり取りするための伝送路のことをバスといい、1クロックでやり取りできるデータ量のことをバス幅といいます。そのため一般的には、クロック周波数が大きく、バス幅が広いほど速く多くのデータをやり取りできます。

レジスタ

ここからはレジスタについて説明していきます。レジスタとはCPU内部の記憶装置であり、高速だが容量が少ないという特徴があります。命令を実行する際に使用されます。レジスタには多くの種類があり、下記がその一部です。

- 命令レジスタ:実行する命令を一時的に格納するレジスタ

- 命令アドレスレジスタ(プログラムカウンタ):次に実行する命令のアドレスを格納するレジスタ

- インデックス(指標)レジスタ:基準となるアドレスを格納するレジスタで、インデックス(指標)アドレス指定方式で使われる。

- ベース(基底)レジスタ:基準となるアドレスを格納するレジスタで、ベース(基底)アドレス指定方式で使われる。

- アキュムレータ:演算の対象や演算の結果を格納する。

- 汎用レジスタ:特定の役割を持たないレジスタで、命令によって各種の目的に使用される。

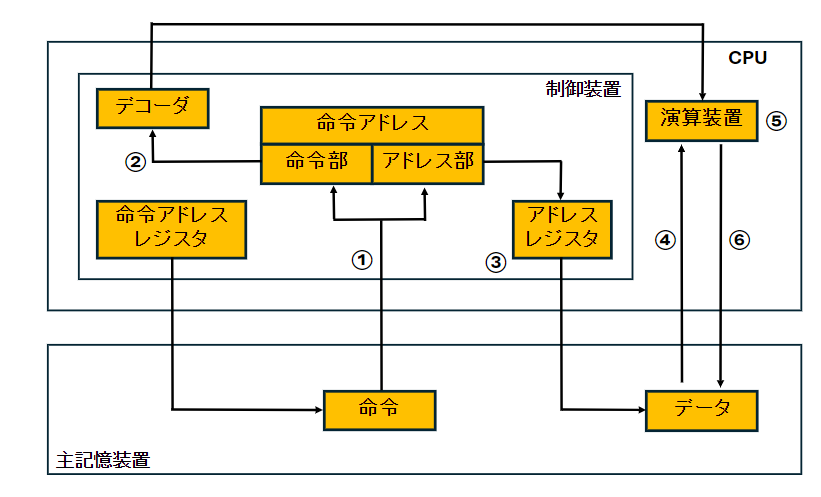

コンピュータが命令を実行する際の流れを命令実行サイクルといい、下記1~6がその段階であり、下図が段階を表として示したものです。下図にある「命令」は命令語であり、命令部とアドレス部で構成されています。命令部では命令や演算、アドレス部では処理対象のデータのアドレスの指示が行われます。

- 命令の取り出し:命令アドレスレジスタ(プログラムカウンタ)を参照し、主記憶装置のアドレスを取得する。取得したアドレスから命令を取り出して命令レジスタに格納する(命令フェッチ)。

- 命令の解読:命令の命令部をデコーダ(解読器)で解読して、演算装置に指示を出す。

- 実効アドレスの計算:命令のアドレス部の値をアドレスレジスタに送り、処理対象のデータが格納されているアドレス(実行アドレス)を計算する。

- オペランドの取り出し:処理対象のデータを取り出して演算装置に送る。

- 命令の実行:演算装置で演算を行う。

- 結果の格納:演算装置で演算した結果を格納する。

アドレス指定方式

ここからはアドレス指定方式について説明していきます。アドレス指定方式とは、命令のアドレス部から処理対象のデータが格納されている実効アドレスを求める方式のことをいいます。アドレス指定方式は6種類あり、説明したものが下記になります。

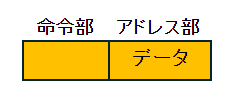

・即値アドレス指定方式:アドレス部に対象のデータがそのものが格納している方式。

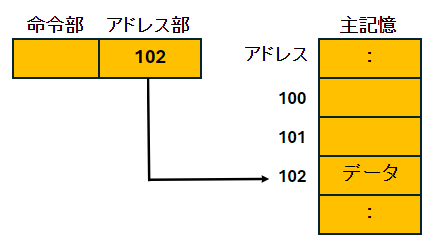

・直接アドレス指定方式:アドレス部の値を実効アドレスとする方式。下図ではアドレス部の102が実効アドレスとなる。

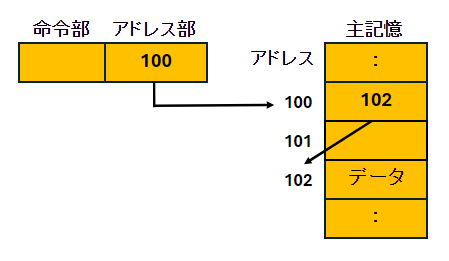

・間接アドレス指定方式:アドレス部の値が示すアドレスに格納された値を実効アドレスとする方式。下図では、主記憶のアドレス100に格納された102が実効アドレスとなる。

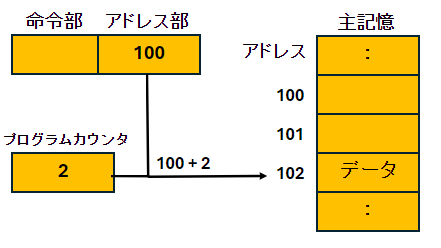

・相対アドレス指定方式:アドレス部の値とプログラムカウンタの値の和を実効アドレスとする方式。下図ではアドレス部の100とプログラムカウンタの2の和である102が実効アドレスとなる。

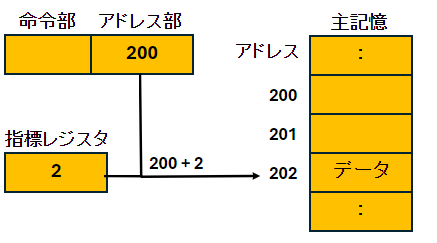

・インデックス(指標)アドレス指定方式:アドレス部の値とインデックス(指標)レジスタの値の和を実効アドレスとする方式。下図ではアドレス部の200と指標レジスタの2の和である202が実効アドレスとなる。

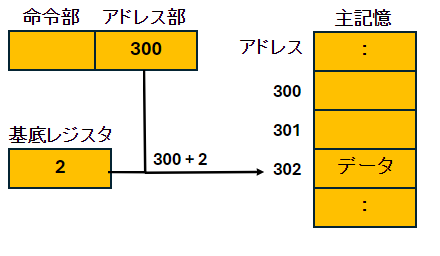

・ベース(基底)アドレス指定方式:アドレス部の値とベース(基底)レジスタの値の和を実効アドレスとする方式。下図ではアドレス部の300と基底レジスタの2の和である302が実効アドレスとなる。

CPUの高速化技術

ここからはCPUの高速化について説明します。まずはステージの実行方式について以下の4つの方式を説明します。

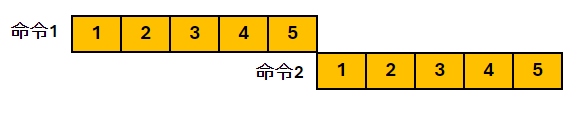

・逐次制御方式:命令を1つずつ順番に繰り返し実行する方式。1つの命令が処理されるまでは次の処理が実行されないため、制御装置や演算装置が動作しない時間ができてしまう。

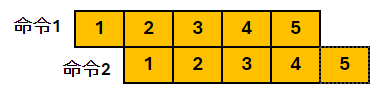

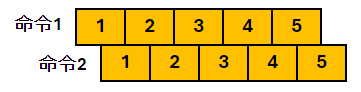

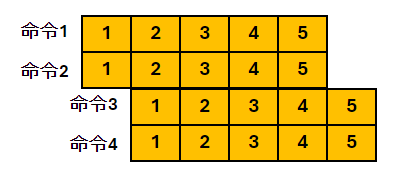

・パイプライン方式:複数の命令を1ステージずつずらしながら同時に処理をする方式。高速化はできるが、命令の分岐がされると新たに分岐先の命令を実効する必要がある。対策として、実行される確率の高い分岐の予測(分岐予測)や予測した分岐先の結果を保持して、分岐先が正しい場合に利用する(投機実行)などがあります。

・スーパーパイプライン方式:パイプライン方式の各ステージをさらに細分化する方式。

・スーパースカラ方式:複数のパイプラインを使い、同時に複数の命令を実行する方式。

・ここからは他の高速化に関連したものについて説明します。

CPUの命令体系ではCISCとRISCというものがあります。CISCは複雑な命令体系で、1つの命令で複雑な処理を行うことができます。RISCは単純な命令体系で、単純な命令に絞ることで1つ1つの命令を高速に処理しています。CISCは主にPCで、RISCは主にスマホなどに使われています。

1つのCPU内に複数のコア(処理を行う部分)を搭載したものをマルチプロセッサといいます。シングルプロセッサ(1つのコア)に比べて消費電力を抑え、処理速度を速めることができます。一方で並列処理(どのコアに何の処理を当てるかなど)のプログラミングが複雑になります。

行列演算を用いて画像処理を高速に実行する装置のことをGPUといいます。近年のCPUにはGPUの機能が統合されています。大量の行列演算を行えることから機械学習の分野で利用されたりもします。

まとめ

CPUの内容だけで結構多くなってしまいました。次はコンピュータ構成要素の続きである記憶装置、入力装置、出力装置について説明しようと思います。

コメント